Бурное развитие цифровой электронной техники позволяет при формировании аналоговых сигналов в большинстве случаев использовать цифровые методы.

Под термином «синтезатор частоты» понимают электронное устройство, способное формировать из опорной частоты на выходе требуемую частоту или набор частот, согласно управляющим сигналам. Наиболее распространенными являются следующие методы синтеза частот:

- прямой аналоговый синтез (Direct Analog Synthesis, DAS) на основе структуры смеситель/фильтр/делитель, при котором выходная частота получается непосредственно из опорной частоты посредством операций смешения, фильтрации, умножения и деления;

- косвенный синтез на основе фазовой автоматической подстройки частоты (Phase Locked Loop, PLL), при котором выходная частота формируется с помощью дополнительного генератора (чаще всего это генератор, управляемый напряжением — Voltage Controlled Oscillator, VCO), охваченного петлей ФАПЧ;

- прямой цифровой синтез (Direct Digital Synthesis, DDS), при котором выходной сигнал синтезируется цифровыми методами;

- гибридный синтез, представляющий собой комбинацию нескольких методов, описанных выше.

Каждый из этих методов синтеза частот имеет преимущества и недостатки, следовательно, для каждого конкретного приложения нужно делать выбор, основанный на наиболее приемлемой комбинации компромиссов. К основным параметрам, характеризующим качество синтезатора частоты, относятся:

- чистота спектра выходного сигнала (уровень побочных компонентов и уровень шума);

- диапазон перестройки (полоса частот выходного сигнала);

- скорость перестройки;

- частотное разрешение;

- количество генерируемых частот;

- гибкость (возможность осуществления разных видов модуляции);

- неразрывность фазы выходного сигнала при перестройке.

В данном курсовом проекте необходимо разработать цифровой генератор сигналов синусоидальной, треугольной и прямоугольной формы.

Обзор существующих цифровых синтезаторов сигналов

1 Прямой аналоговый синтез

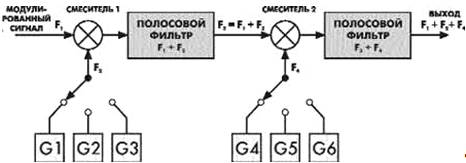

Структурная схема прямого аналогового синтезатора показана на рисунке 1. Этот метод синтеза называют прямым, потому что в нем отсутствует процесс коррекции ошибки. Следовательно, качество выходного сигнала напрямую связано с качеством опорного сигнала. Фазовый шум такого синтезатора достаточно низок вследствие прямого синтеза. Перестройка по частоте может быть очень быстрой

Измерение частоты сигнала с помощью электронно-лучевого осциллографа

... пикосекундной длительности), для чего используется специальная электронно-лучевая трубка бегущей волны. Предварительного усиления входного сигнала в скоростных осциллографах, как правило, не производят, поэтому чувствительность ... ранее, следующей зависимостью: (1). Динамическая чувствительность на частотах обращается в нуль. Частоту называют критической; она зависит от значения ускоряющего напряжения ...

Рисунок 1 — Структурная схема DAS

Одной из важных особенностей DAS-синтезатора (от англ.: Direct Analog Synthesis — прямой аналоговый синтез) на основе смесителя/фильтра является возможность вернуться на любую частоту и продолжать работать в той же фазе, как если бы перехода не было вообще. Этот эффект называют «фазовой памятью».

Для перестройки по частоте используется переключаемый банк опорных генераторов. Это удобно, например, для радиостанций с небольшим количеством каналов. Но для перекрытия широкого диапазона частот потребуется большое количество опорных генераторов, что является весьма дорогостоящим решением.

Используя делители частоты, имеющие структуру смеситель — фильтр — делитель, можно уменьшить количество необходимых опорных генераторов, хотя и в этом случае возможности перестройки останутся более чем скромными.

2 Косвенный синтез частоты на основе фазовой автоподстройки

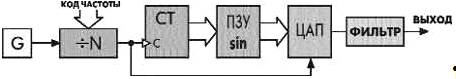

Этот метод синтеза использует принцип сравнения частоты и фазы выходного сигнала, формируемого VCO (от англ.: Voltage Controlled oscillator — генератор управляемый напряжением), с сигналом опорного генератора. Структурная схема такого синтезатора показана на рисунке 2.

Рисунок 2 — Структурная схема PLL

Обнаружение ошибки обеспечивает фазовый детектор (ФД), который работает на определенной частоте Fс, называемой частотой сравнения. Эта частота получается путем деления частоты опорного генератора G на N. Частота выходного сигнала вначале делится на M, а затем сравнивается с частотой Fс. При отклонении частоты на выходе ФД появляется управляющее напряжение, воздействующее на управляющий элемент VCO до исчезновения отклонения. Поскольку делители частоты имеют целочисленные коэффициенты деления, шаг сетки такого синтезатора определяет частота сравнения. Выходная частота определяется по формуле:

F OUT = FC ∙ M = (FCLK /N) ∙ M = FCLK ∙ (N/M),

где F OUT — выходная частота;C — частота сравнения;

- коэффициент деления опорной частоты;

- коэффициент деления выходной частоты.

Другими словами, PLL-синтезатор (от англ.: Phase Locked Loop — петля с заблокированной фазой, т.е. косвенный синтез на основе фазовой автоподстройки частоты) умножает опорную частоту в N/M раз.

Коэффициенты N и M могут задаваться микроконтроллером, хотя на практике число N при перестройке меняют редко, так как это влечет за собой изменение частоты сравнения (и, соответственно, шага сетки) и требует изменения параметров петлевого фильтра.

Фазовый детектор является источником дополнительных фазовых шумов. Попытка получить малый шаг перестройки частоты вынуждает работать на более низкой частоте сравнения, что требует понижения частоты среза петлевого фильтра. А это еще более увеличивает фазовые шумы. Быструю перестройку частоты в таком синтезаторе обеспечить также очень сложно.

Цифровые синтезаторы частоты

... синтезаторам частот косвенного синтеза. Диапазон перестройки такого синтезатора может быть непрерывным от долей Гц до десятков МГц, при этом точность установки частоты и шаг перестройки составляет сотые доли Гц, а скорость перестройки частоты ... исключением ЦАП) называется генератором с цифровым управлением (NCO). Выпускаются и микросхемы NCO, в состав которых не входит, по сравнению с DDS, только ...

Для получения малого шага перестройки по частоте иногда объединяют в одном синтезаторе несколько петель PLL. Однако многопетлевой PLL-синтезатор является весьма дорогим и громоздким устройством, что сдерживает его широкое применение.

1.3 Прямой цифровой синтез

Прямой цифровой синтез — относительно новый метод синтеза частоты, появившийся в начале 70-х годов прошлого века. Все описанные методы синтеза доступны разработчикам уже десятилетия, но только в последнее время DDS (от англ.: Direct Digital Synthesis — прямой цифровой синтез) уделяется пристальное внимание. Появление дешевых микросхем с DDS и удобных средств разработки делает их сегодня привлекательными для разных сфер применения.уникальны своей цифровой определенностью — генерируемый ими сигнал синтезируется со свойственной цифровым системам точностью. Частота, амплитуда и фаза сигнала в любой момент времени точно известны и подконтрольны. DDS практически не подвержены температурному дрейфу и старению. Единственным элементом, который обладает свойственной аналоговым схемам нестабильностью, является ЦАП (Цифро-аналоговый преобразователь).

Высокие технические характеристики стали причиной того, что в последнее время DDS вытесняют обычные аналоговые синтезаторы частот.

3.1 Основные преимущества прямого цифрового синтеза

- очень высокое разрешение по частоте и фазе, управление которыми осуществляется в цифровом виде;

- экстремально быстрый переход на другую частоту (или фазу), перестройка по частоте без разрыва фазы, без выбросов и других аномалий, связанных со временем установления;

- архитектура, основанная на DDS, ввиду очень малого шага перестройки по частоте, исключает необходимость применения точной подстройки опорной частоты, а также обеспечивает возможность параметрической температурной компенсации;

- цифровой интерфейс позволяет легко реализовать микроконтроллерное управление;

- для квадратурных синтезаторов имеются DDS с I и Q выходами, которые работают согласованно.

Частотное разрешение DDS составляет сотые и даже тысячные доли герца при выходной частоте порядка десятков мегагерц. Такое разрешение недостижимо для иных методов синтеза. Другой характерной особенностью DDS является очень высокая скорость перехода на другую частоту. Синтезаторы на основе PLL используют обратную связь и фильтрацию сигнала ошибки, что замедляет процесс перестройки частоты. Для DDS скорость перестройки ограничена практически только быстродействием цифрового управляющего интерфейса. Более того, все перестройки по частоте в DDS происходят без разрыва фазы выходного сигнала. Поскольку выходной сигнал синтезируется в цифровом виде, очень просто можно осуществить модуляцию различных видов.

Параметры синтезатора частоты очень важны для аппаратуры связи. Являясь сердцем системы настройки, синтезатор в основном определяет потребительские свойства конкретного аппарата. Как с технической, так и с экономической стороны DDS удовлетворяет большинству критериев идеального синтезатора частоты: простой, высокоинтегрированный, с малыми габаритами. Кроме того, многие параметры DDS программно-управляемые, что позволяет заложить в устройство новые возможности. Современные DDS используют субмикронную CMOS-технологию, трехвольтовую логику, миниатюрные корпуса. Одновременно постоянно снижаются цены на них. Все это делает DDS очень перспективными приборами.

Генератор звуковых частот

... генераторов, являются: источник исходного сигнала (перестраиваемый автогенератор или кварцевый синтезатор частоты), усилители, выходные формирователи сигнала, выходной аттенюатор, цепи управления, цепи стабилизации выходного ... Свип-генератор (от англ. sweep — размах, непрестанное движение), генератор качающейся частоты, генератор измерительный, на выходе которого частота электрических колебаний ...

С процессами дискретизации и цифро-аналогового преобразования, которые имеют место в DDS, связаны и некоторые ограничения:

- максимальная выходная частота не может быть выше половины тактовой (на практике она еще меньше).

Это ограничивает области применения DDS областями HF (от англ.: High frequency — высокая частота) и части VHF-диапазона;

- (от англ.: Very high frequency — очень высокая частота)

- отдельные побочные составляющие выходного на выходе DDS могут быть значительными, по сравнению с синтезаторами других типов. Спектральная чистота выходного сигнала DDS сильно зависит от качества ЦАП;

— потребляемая DDS-мощность практически прямо пропорциональна тактовой частоте и может достигать сотен милливатт. При больших тактовых частотах DDS могут оказаться непригодными для устройств с батарейным питанием.

3.2 Структура процесса прямого цифрового синтеза

Если сразу рассматривать реальную структуру конкретного DDS, то она может показаться необоснованно сложной и запутанной. Для того чтобы та или иная особенность структуры DDS была очевидной, начнем рассмотрение с конечного результата, который нужно получить.

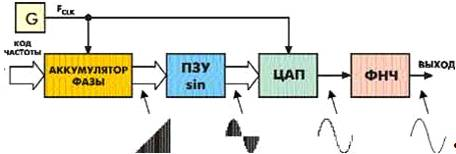

Задача DDS — получить на выходе сигнал определенной формы заданной частоты. Поскольку в DDS формирование выходного сигнала происходит в цифровой форме, совершенно очевидна необходимость цифро-аналогового преобразования. Это означает, что в структуре DDS должен быть ЦАП. В любом случае на выходе ЦАП должен присутствовать фильтр нижних частот (ФНЧ) для подавления периодически повторяющихся образов выходного спектра — FCLK (от англ.: anti-aliasing filter clock — сглаживающий фильтр).

Для получения синусоидального, треугольного или прямоугольного сигнала на входе ЦАП необходимо подать последовательность отсчетов функции, следующих с частотой дискретизации FCLK. Законы изменения функций во времени различны, но определенные затруднения вызывает только синусоидальный сигнал и цифровыми методами просто не реализуется. Поэтому наиболее подходящим методом формирования отсчетов функций является табличный метод. Перекодировочная таблица (Look Up Table) чаще всего размещается в постоянном запоминающем устройстве (ПЗУ).

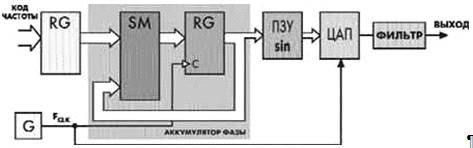

Код, который подается на адресные входы ПЗУ, является аргументом функции, а выходной код ПЗУ равен значению функции для данного аргумента. Аргумент функции или фаза, в отличие от значения функции, меняется во времени линейно. Сформировать линейно меняющуюся во времени последовательность кодов гораздо проще. Это способен сделать простой двоичный счетчик. Поэтому простейший DDS выглядит так: двоичный счетчик формирует адрес для ПЗУ, куда записана таблица одного периода функции, отсчеты с выхода ПЗУ поступают на ЦАП, который формирует на выходе определенный сигнал, подвергающийся фильтрации в ФНЧ и поступающий на выход (рисунок 3).

Для перестройки выходной частоты используется делитель с переменным коэффициентом деления, на вход которого поступает тактовый сигнал с опорного генератора.

Исследование радиотехнических сигналов

... сигнала. Фаза n — ой гармоники, характеризующую фазу спектральных составляющих, определяется по формуле: Так как сигнал периодический, он имеет линейчатый спектр, представленный набором гармоник с частотами, кратными частоте ... 1,35 212 67,13 Рисунок 5 — АЧХ периодического сигнала Рисунок 6 — ФЧХ периодического сигнала 3.2 Построение АЧХ и ФЧХ спектра непериодического сигнала Ряд Фурье справедлив для ...

Рисунок 3 — Структурная схема DDS с адресным счетчиком ПЗУ

Кроме того, при перестройке выходной частоты будет меняться и частота дискретизации. Это затрудняет фильтрацию выходного сигнала, а также ведет к неоптимальному использованию скоростных характеристик ЦАП — они будут в полной мере использованы лишь на максимальной выходной частоте. Гораздо логичнее всегда, независимо от выходной частоты, работать на постоянной частоте дискретизации, близкой к максимальной для используемого ЦАП.

Все недостатки описанной выше структуры могут быть устранены путем введения одного, но весьма оригинального решения — заменить адресный счетчик ПЗУ другим цифровым устройством, которое называется накапливающим сумматором. Накапливающий сумматор представляет собой регистр, который в каждом такте работы устройства перезагружается величиной, равной старому содержимому, плюс некоторая постоянная добавка (рисунок 4).

Когда накапливающий сумматор используется для формирования кода фазы, его еще называют аккумулятором фазы. Выходной код аккумулятора фазы представляет собой код мгновенной фазы выходного сигнала. Постоянная добавка, которая используется при работе аккумулятора фазы, представляет собой приращение фазы за один такт работы устройства. Чем быстрее изменяется фаза во времени, тем больше частота генерируемого сигнала. Поэтому значение приращения фазы фактически является кодом выходной частоты.

Рисунок 4 — Структурная схема DDS с аккумулятором фазы

Действительно, если приращение фазы равно единице, то поведение накапливающего сумматора ничем не отличается от поведения двоичного счетчика. Но если приращение фазы будет равно, например, двум, то код фазы будет изменяться вдвое быстрее. При этом на ЦАП коды будут поступать с той же частотой, но будут представлять собой не соседние, а взятые через один отсчеты функции sin. Частота генерируемого сигнала при этом будет вдвое большей, а частота дискретизации останется прежней. Аккумулятор фазы работает с периодическими переполнениями, обеспечивая арифметику по модулю 2N. Такое периодическое переполнение соответствует периодическому поведению функции sin с периодом 2p. Другими словами, частота переполнения аккумулятора фазы равна частоте выходного сигнала. Это частота определяется формулой:

F OUT = M ∙ FCLK /2N ,

Где F OUT — выходная частота;CLK — тактовая частота;

- код частоты;

- N — разрядность аккумулятора фазы.

По существу, тактовая частота делится на некоторое число, которое определяется кодом частоты и разрядностью аккумулятора фазы. При этом шаг перестройки частоты не зависит от ее значения.

Из этого следует еще одно уникальное свойство синтезатора частоты на основе накапливающего сумматора: если увеличить разрядность N, то уменьшится шаг перестройки частоты. Причем особых ограничений здесь нет. Например, если разрядность накапливающего сумматора 32 бита, а тактовая частота составляет 50 МГц, то частотное разрешение составит порядка 0,01 Гц. Увеличение разрядности аккумулятора фазы в данном случае повлечет за собой увеличения разрядности адреса ПЗУ. При реализации синусоидального сигнала для адресации можно использовать лишь необходимое количество старших разрядов кода фазы, но для треугольного и прямоугольного сигнала понадобиться соответствие разрядов.

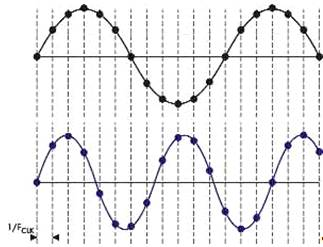

Таким образом, в DDS аккумулятор фазы формирует последовательность кодов мгновенной фазы сигнала, которая изменяется линейно (рисунок 5).

Скорость изменения фазы задается кодом частоты. Далее с помощью ПЗУ линейно изменяющаяся фаза преобразуется в изменяющиеся по определенному закону отсчеты выходного сигнала. Эти отсчеты поступают на ЦАП, на выходе которого формируется сигнал, состоящий из «ступенек». Они фильтруются аналоговым ФНЧ, и на его выходе получается записанный в ПЗУ сигнал.

Рисунок 5 — Схема изменения сигналов в DDS с аккумулятором фазы

Выходной сигнал восстанавливается из отдельных отсчетов. Целое число отсчетов на период укладывается лишь в частном случае. В большинстве случаев это не так, и на каждом новом периоде сигнала отсчеты находятся в новых местах (рисунок 6).

Конечно, картина периодически повторяется, но период повторения может быть самым разным. Он зависит от кода частоты, разрядности аккумулятора фазы и от разрядности используемого кода фазы. В любом случае с равным успехом из последовательности отсчетов будет восстановлен сигнал заданной формы.

Рисунок 6 — Синусоидальный выходной сигнал с DDS

Рассмотренная выше структура применяется во всех современных DDS. Объединение в одном чипе быстродействующего ЦАП и собственно DDS (так называемый полный DDS или CoMplete DDS) позволило получить весьма заманчивую альтернативу обычным синтезаторам на основе PLL. DDS, не имеющие встроенного ЦАП, иногда называют NCO (от англ.: NuMerically Controlled Oscillator — осциллятор с числовым управлением), несмотря на то, что DDS не содержит никаких генераторов.

2. Создание структурной схемы генератора

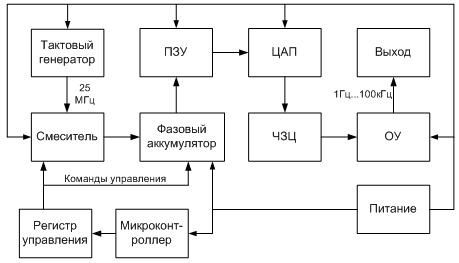

Составим структурную схему для цифрового генератора на основе микросхемы цифрового синтеза частоты (рисунок 7).

Рисунок 7 — Структурная схема цифрового генератора сигналов

Тактовый генератор обеспечивает формирование управляющих импульсов заданной частоты, необходимой для использования всего заданного спектра частот, от 1 Гц до 100кГц;

- Микроконтроллер передает управляющие сигналы на регистр управления;

- Цифровой синтезатор принимает подаваемые микроконтроллером команды управления и подстраивает частоту и фазу в соответствии с командами.

Цифроаналоговый преобразователь преобразует цифровое значение уровня сигнала в аналоговый уровень сигнала.

Тактовый генератор формирует сигнал с частотой 25 МГц, который поступает на смеситель частоты, куда приходит управляющие сигналы с контроллера, в результате смеситель на основе опорной частоты формирует сигнал заданной частоты. После этого сигнал со смесителя поступает на аккумулятор фазы, где рассчитывается значение фазы, в соответствии со значением частоты и числом М, определяющим фазовую надбавку.

Потом сигнал складывается с фазовым сдвигом заданным в фазовом регистре, после чего поступает либо на ПЗУ, либо идет в обход него, в зависимости от регистра управления, только после этого сигнал поступает на ЦАП и затем на фильтр нижних частот.

3. Описание функциональной схемы устройства

Составим функциональную схему для многофункционального цифрового генератора на основе микросхемы цифрового синтеза частоты.

Рисунок 8 — Функциональная схема многофункционального цифрового генератора

Тактовый генератор обеспечивает формирование управляющих импульсов заданной частоты, необходимой для использования всего заданного спектра частот, от 1 Гц до 100кГц;

- Микроконтроллер передает управляющие сигналы на регистр управления;

Смеситель преобразует частоту тактового генератора до частоты заданной

Регистр управления принимает команды микроконтроллера и подает управляющие сигналы на смеситель и фазовый аккумулятор;

- Фазовый аккумулятор прибавляет заданную регистром управления фазовую надбавку к сигналу.

Пользовательское запоминающее устройство (ПЗУ) хранит значения функции синуса для каждого из возможных значений фазы.

Цифроаналоговый преобразователь (ЦАП) преобразует цифровое значение уровня сигнала в аналоговый уровень сигнала.

Частотно-зависимая цепь на выходе ЦАП выполняет роль фильтра нижних частот и сглаживает нелинейность сигнала, а также служит для урегулирования уровней входного сопротивления операционного усилителя (ОУ) и выходного сопротивления ЦАП.

Операционный усилитель (ОУ) усиливает выходной сигнал синтезатора до необходимого уровня.

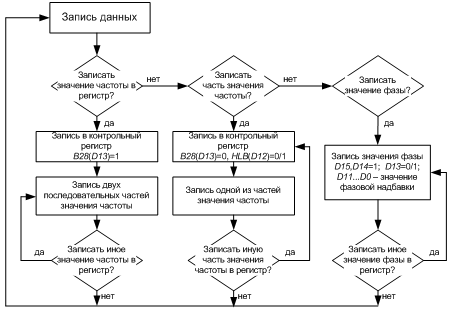

4. Алгоритмы работы устройства

Алгоритм записи данных в устройство изображен на рисунке 9.

Рисунок 9 — Алгоритм записи данных в устройство

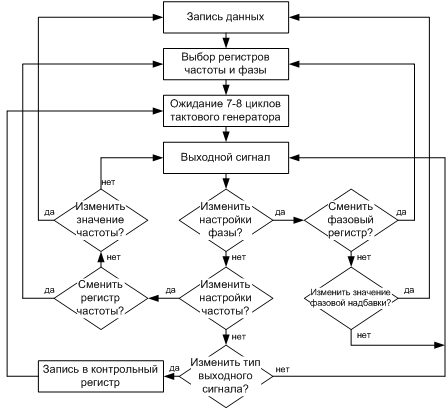

Алгоритм работы устройства представлен ниже (рисунок 10), он отображает функционирование многофункционального цифрового генератора в режиме реального времени.

Рисунок 10 — Алгоритм работы устройства

5. Описание основных элементов

1 Цифровой синтезатор частоты AD9833

Синтезатор ИС AD9833, управляется посредством быстродействующего последовательного порта SPI, при этом для генерации синусоидального сигнала требуется только тактовый сигнал. Доступные в настоящее время синтезаторы DDS способны генерировать сигнал на частотах от 1 Гц до 400 МГц (при тактовой частоте 1 ГГц).

Преимущества, предоставляемые малым энергопотреблением, низкой стоимостью и малыми размерами корпусов, в сочетании с отличным качеством сигнала и возможностью цифрового управления, делают синтезаторы DDS чрезвычайно привлекательными приборами по сравнению с гораздо менее гибкими схемами на дискретных элементах.

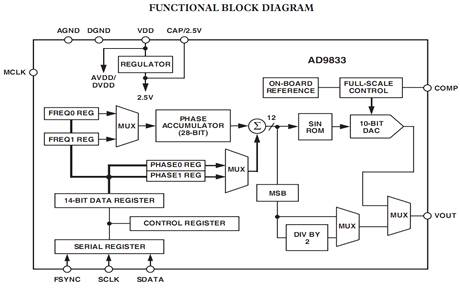

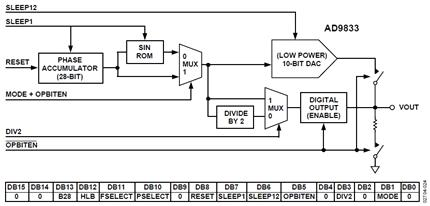

На рисунке 11 показана функциональная схема AD9833: его основными узлами являются накопитель значения фазы (аккумулятор фазы), средство преобразования значения фазы в амплитуду (обычно это ПЗУ с табличными значениями функции) и ЦАП. Схема DDS генерирует сигнал с заданной частотой. Частота выходного сигнала определяется двумя параметрами: частотой тактового сигнала и двоичным числом, записанным в регистр частоты. Это двоичное число, записанное в регистр частоты, подается на вход аккумулятора фазы. Если используется ПЗУ с табличными значениями, то аккумулятор фазы вычисляет адрес (соответствующий мгновенному значению фазы) и подает его на вход ПЗУ, при этом на выходе ПЗУ мы получаем текущее значение амплитуды в цифровом виде. Далее ЦАП преобразует это цифровое значение в соответствующее значение напряжения или тока. Для генерации сигнала с фиксированной частотой постоянная величина (приращение фазы, определяемое двоичным числом, записанным в регистр частоты) прибавляется к значению, хранящемуся в аккумуляторе фазы, с каждым импульсом тактового сигнала. Если значение приращения велико, аккумулятор фазы будет быстро пробегать всю таблицу значений, хранящуюся в ПЗУ, и частота сигнала при этом будет высока. Если значение приращения фазы мало, аккумулятору фазы понадобится больше шагов, чтобы пройти всю таблицу ПЗУ, и соответственно частота сигнала на выходе будет низкой. Мгновенное значение фазы непрерывного синусоидального сигнала циклически изменяется в диапазоне от 0 до 2π. Значение фазы генерируется в цифровом виде. Функция переноса, которой обладает счетчик, позволяет реализовать в синтезаторе DDS непрерывное циклическое изменение величины фазы.

цифровой синтезатор микроконтроллер аналоговый

Рисунок 11 — Функциональная схема двухканального цифрового синтезатора AD9833

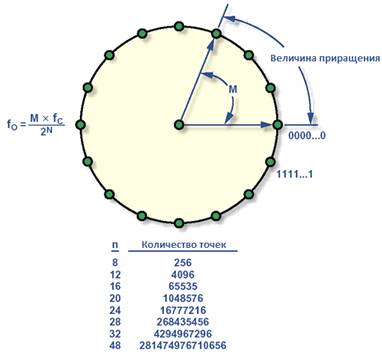

Принцип генерации сигналов изображен на рисунке 12. Каждая точка на окружности соответствует определенной точке функции. Один оборот вектора с постоянной скоростью обеспечивает генерацию одного периода сигнала. Аккумулятор фазы генерирует значения сигнала с одинаковыми приращениями, величина, находящаяся в аккумуляторе фазы, соответствует определенной точке окружности.

Рисунок 12 — Циклическое вычисление значения сигнала

Аккумулятор фазы представляет собой счетчик по модулю М, значение которого увеличивается с каждым приходом тактового импульса. Величина приращения задается двоичным числом М. Это число определяет величину приращения значения фазы с каждым тактовым импульсом, в сущности этим числом определяется число пропущенных отсчетов при движении по окружности. Чем больше размер шага, тем быстрее происходит переполнение аккумулятора фазы и более коротким получается период синусоиды. Разрядностью аккумулятора фазы (n) определяется общее число возможных значений фазы, что в свою очередь определяет разрешение сетки частот синтезатора DDS. Для 8-разрядного аккумулятора фазы при М = 00000001 аккумулятор будет переполняться после 255 циклов (тактовых импульсов).

При М = 01111111 аккумулятор фазы будет переполняться всего за 2 цикла (это минимальное число циклов, удовлетворяющее критерию Найквиста).

Эти соотношения описываются

,

,

где f out — частота выходного сигнала DDS;

- М — двоичное число, определяющее частоту сигнала;

- c — частота сигнала тактирования;

- разрядность аккумулятора фазы.

При изменении значения М частота на выходе синтезатора меняется сразу, и при этом сигнал не имеет разрывов. Здесь отсутствует переходный процесс захвата частоты, присущий генераторам с петлёй ФАПЧ. При увеличении выходной частоты число отсчётов на один цикл уменьшается. Так как теорема отсчетов требует наличия как минимум двух отсчетов на период для полного восстановления выходного сигнала, то максимальная частота синтезируемого сигнала DDS будет составлять f c /2. Однако на практике частота синтезируемого сигнала ограничивается несколько меньшим значением, что способствует улучшению качества синтезируемого сигнала и облегчению его фильтрации.

При генерировании сигнала постоянной частоты код на выходе аккумулятора фазы увеличивается по линейному закону, что соответствует линейному треугольному аналоговому сигналу. Для преобразования выходного кода аккумулятора фазы (в случае ИС AD9833 — это 28-разрядный код) в мгновенные значения амплитуды используется ПЗУ с табличными значениями отсчетов функции. Младшие разряды 28-разрядного кода отбрасываются; на выходе табличного ПЗУ мы получаем 10-разрядный код, который подаётся на ЦАП. Т.к. синусоида обладает симметричностью, в синтезаторе DDS хранятся табличные данные только об ¼ части синусоиды. Табличное ПЗУ генерирует полный цикл синусоиды за счет чтения данных сначала в прямом, затем в обратном порядке.

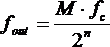

5.1.1 Регистр управления цифрового синтезатора частоты AD9833

Микросхема AD9833 содержит 16-разрядный регистр управления, который позволяет управлять деятельностью цифрового синтезатора.

Вид 16-разрядного регистра и схематичное функционирование его отдельных битов изображено на рисунке 13.

Рисунок 13 — Функции отдельных битов управляющего регистра

В таблице 1 подробно описаны значение функций отдельных битов управляющего регистра.

Таблица 1 Описание битов управляющего регистра

|

Бит |

Описание функции |

|

|

D13 |

B28 |

Для записи значения в регистр частоты необходимо загрузить два полных слова управления. B28=1 позволяет загрузить полное слово в регистр частоты через две последовательные записи. Первая из которых содержит 14 младших битов слова частоты, а вторая — 14 старших. Первые 2 бита слова определяют в какой из 2х регистров частоты будет загружено значение. Запись в регистр частоты происходит после того, как оба слова были введены, поэтому регистр никогда не удерживает промежуточное значение. Если B28=0, то 28-разрядный регистр частоты работает как 2 отдельных 14-разрядных регистра. Это означает, что младшая часть может быть заменена независимо от старшей, так же возможно и обратное. |

|

D12 |

HLB |

Этот бит управления позволяет пользователю последовательно загрузить младшую или старшую часть слова частоты. Эта возможность используется когда, не требуются все 28 разрядов для установки значения частоты. Для того чтобы раздельно менять части слова частоты необходимо установить D13(B28)=0, а также для возможности записи старшей части D12(HLB)=1, а для записи младшей — D12(HLB)=0. |

|

D11 |

FSELECT |

Бит определяет, какой из регистров частоты управляет фазовым аккумулятором. Если FSELECT=0, то выбран нулевой регистр частоты и наоборот. |

|

D10 |

PSELECT |

Бит определяет, данные из какого регистра фазы будут складываться со значением на выходе фазового аккумулятора. Если PSELECT=0, то выбран нулевой фазовый регистр и наоборот. |

|

D9 |

RESERVED |

Этот бит всегда равен 0. |

|

D8 |

RESET |

RESET=1 обнуляет значение внутренних регистров. И создает на выходе сигнал среднего уровня. |

|

D7 |

SLEEP1 |

Когда SLEEP1=1, то внутренние цифровые часы отключаются, и выходной сигнал ЦАП остается неизменным, т.к. на вычисления на встроенном осцилляторе прекращаются. |

|

D6 |

SLEEP12 |

Когда SLEEP12=1, ЦАП отключен, и на выход поступает величина MSB, равная старшей части данных, бывших на ЦАП в момент отключения. |

|

D5 |

OPBITEN |

Функцией данного бита совместно в битом D1(MODE) является управление формой выходного сигнала. Когда OPBITEN=1, на выход поступает старшая часть данных, поступающих на ЦАП или их половина, в зависимости от бита D3(DIV2).

|

|

D4 |

RESERVED |

Этот бит всегда равен 0. |

|

D3 |

DIV2 |

Используется совместно с битом D5(OPBITEN). Когда DIV2=1, на выход поступает величина равная MSB, то есть полная старшая часть байта, если же DIV2=0, то на выход поступает величина, равная MSB/2. |

|

D2 |

RESERVED |

Этот бит всегда равен 0. |

|

D1 |

MODE |

Этот бит используется совместно с D5(OPBITEN), его функцией является управление формой выходного сигнала при включенном ЦАП. Когда MODE=1, ПЗУ не участвует в формировании выходного сигнала и на выходе мы получаем треугольную форму сигнала, если MODE=0, то ПЗУ активно и форма выходного сигнала — синусоида. |

|

D0 |

RESERVED |

Этот бит всегда равен 0. |

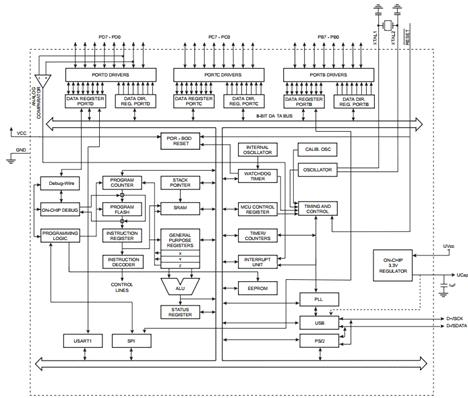

.2 Микроконтроллер AT90USB162

AT90USB162 — маломощный 8-разрядный комплиментарный-металлооксидный полупроводник (КМОП) микроконтроллер, выполненный на основе прогрессивной RISC-архитектуре (от англ.: restricted (reduced) instruction set computer — компьютер с сокращённым набором команд) AVR (семейство микроконтроллеров).

За счет выполнения большинства инструкций за один машинный цикл AT90USB82/162 достигает производительности 1 миллион операций в секунду на МГц тактовой частоты, что позволит разработчикам оптимизировать соотношение потребляемой мощности и производительности.

Ядро AVR объединяет обширный набор инструкций с 32 рабочими регистрами общего назначения. Все 32 регистра напрямую подключены арифметико-логическому устройству (АЛУ), что позволяет указывать в одной инструкции два регистра и выполнять такую инструкцию за один цикл синхронизации. Результирующая архитектура отличается улучшенной эффективностью программного кода и на порядок превосходит по производительности традиционные CISC-микроконтроллеры (от англ.: complex instruction set computer — компьютер с комплексным набором команд).

Микроконтроллеры AT90USB82, AT90USB16 содержат 8/16 кбайт внутрисистемно-программируемой флэш-памяти с поддержкой возможности чтения во время программирования, 512 байт ЭСППЗУ, 512 байт статического оперативного запоминающего устройства (ОЗУ), 22 линии ввода-вывода общего назначения, 32 рабочих регистра общего назначения, два универсальных таймера-счетчика с режимами сравнения и широтно-импульсной модуляции (ШИМ), один универсальный синхронный и асинхронный последовательный приемопередатчик (УСАПП), программируемый сторожевой таймер с внутренним генератором, последовательный порт SPI, отладочный интерфейс «debugWIRE» (используется для доступа к встроенной отладочной системе).

Микроконтроллер также может быть программно переведен в один из пяти режимов работы с пониженным потреблением. В режиме холостого хода (Idle) останавливается центральное процессорное устройство (ЦПУ), но продолжают работу статическое ОЗУ, таймеры-счетчики, порт SPI и система прерываний. В режиме снижения мощности (Power-down) сберегается содержимое регистров, но останавливается тактовый генератор, отключая все встроенные функциональные блоки до следующего прерывания или аппаратного сброса. В дежурном режиме (Standby) остается в работе кварцевый генератор, а остальная часть микроконтроллера бездействует. Использование этого режима позволяет добиться быстроты возобновления работы в сочетании с малым потреблением. В расширенном дежурном режиме (Extended Standby) остается в работе основной генератор.

Микроконтроллеры выпускаются по технологии высокоплотной энергонезависимой памяти компании AtMel. Встроенная ISP флэш-память поддерживает возможности внутрисистемного программирования через интерфейс SPI, программирования с помощью программатора обычной энергонезависимой памяти или программирования под управлением программы в загрузочном секторе и исполняемой ядром AVR. Загрузочная программа может использовать любой интерфейс для загрузки программного кода и размещения его в секторе прикладной программы флэш-памяти. При этом, поддерживается возможность продолжения выполнения программы в загрузочном секторе во время обновления сектора прикладной программы, тем самым, обеспечивая действительную поддержку чтения во время программирования. Объединение 8-разрядного RISC ЦПУ с внутрисистемно-самопрограммируемой флэш-памятью в одном кристалле делает микроконтроллеры AT90USB82, AT90USB16 эффективным инструментом для гибкого и выгодного в стоимостном плане решения многих задач встраиваемого управления.

Структурная схема микроконтроллера изображена на рисунке 14.

Рисунок 14 — Структурная схема микроконтроллера

Микроконтроллеры AT90USB82, AT90USB16 поддерживаются полным набором аппаратных и программных средств для проектирования, в т.ч. Си-компиляторы, макроассемблеры, программные отладчики, симуляторы, внутрисхемные эмуляторы и оценочные наборы.

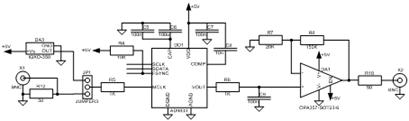

.3 Аналоговая часть схемы

Схема аналоговой части изображена на Рисунке 15. Блокировочные конденсаторы и их номиналы взяты непосредственно из технического описания на микросхему AD9833, они должны быть обязательно установлены. На схеме предусмотрен джампер выбора источника тактовых сигналов, поэтому тактовый сигнал может подаваться либо от осциллятора установленного на плате, либо от внешнего источника через коннектор BNC.

Рисунок 15 — Аналоговая часть цифрового генератора

Выходной сигнал микросхемы AD9833 проходит через фильтр низких частот и поступает на вход операционного усилителя (ОУ).

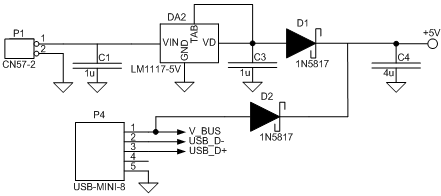

Резистор R10 сопротивлением 50 Ом предназначен для согласования. Операционный усилитель OPA357 в аналоговой части предназначен для усиления выходного сигнала микросхемы AD9833, т.к. ее номинальное выходное напряжение составляет 0.6В с центром на уровне 0.3В. Выбор данного ОУ связан с его возможностью работать на высоких частотах. На рисунке 16 изображена часть аналоговой схемы устройства, отвечающая за питание генератора. Устройство может питаться от интерфейса USB или от внешнего стабилизированного источника 5В. В данном случае применен интегральный регулятор напряжения серии LM1117.

Рисунок 16 — Схема питания цифрового генератора

Два диода Шоттки выполняют защитную функцию при подаче напряжения питания одновременно от двух источников.

6. Выбор элементной базы

В соответствии с указанными в технической документации рекомендациями подберем элементы, необходимые для правильного функционирования цифрового генератора синусоидальных, треугольных и прямоугольных импульсов.

В качестве микросхемы цифрового синтезатора выберем микросхему AD9833, характеристики:

- Потребляемая мощность 12.65 мВт

- Диапазон выходных частот от 0 МГц до 12.5 МГц

- Разрешение частного диапазона 28 бит

- Синусоидальные, треугольные и прямоугольные выходные колебания

- Напряжение питания от 2.3 В до 5.5 В

Исходя из технического описания микросхемы, подберем вспомогательные элементы.

Из ряда Е12 выберем стандартные значения сопротивления резисторов R5 и R6 , равные R5 = R6 = 1 кОм. Выберем тип резисторов С2-3 с допуском 10%.

Из ряда Е12 выберем стандартные значения емкости конденсаторов С5 , С7 , С9 равные, С5 = С7 = С9 = 100 нФ. Выберем тип конденсатора К50-2 с допуском 10%.

Из ряда Е12 выберем стандартное значение емкости конденсатора и

С6 = 100 мкФ. Выберем тип конденсатора К50-2 с допуском 10%.

Из ряда Е12 выберем стандартное значение емкости конденсатора и

С8 = 10 нФ. Выберем тип конденсатора К50-2 с допуском 10%.

Для усиления выходного сигнала цифрового синтезатора выберем операционный усилитель OPA357-SOT23-6, его характеристики:

- Частотный диапазон до 250 МГц

- Максимальный выходной ток 100мА

- Напряжение питания от 2.5 до 5.5 В

- Ток смещения 3 пА

- Максимальный коэффициент усиления 50000

- Минимальный входной ток 4.9 мА

Исходя из технического описания микросхемы, подберем вспомогательные элементы.

Из ряда Е12 выберем стандартное значение сопротивления резистора

R7 = 20 кОм. Выберем тип резисторов С2-2 с допуском 10%.

Из ряда Е12 выберем стандартное значение сопротивления резистора

R8 = 170 кОм. Выберем тип резисторов С2-2 с допуском 10%.

Для ослабления сигналов, проходящих через разъемы BNC, установим перед ними предохранительные резисторы.

Из ряда Е12 выберем стандартные значения сопротивления резисторов

R12 = R10 = 50 Ом. Выберем тип резисторов С2-6 с допуском 10%.

Для защиты схемы установим после источников питания диоды Шоттки. Выберем тип диода 1N5817, с максимальным рабочим напряжением, равным 5В.

Характеристики микроконтроллера AT90USB162:

- Ядро AVR

- Частота ЦПУ 16 МГц

- Flash память 16 КБайт

- ОЗУ 0.5 Кбайт

- ПЗУ 0.5 Кбайт

- Интерфейсы SPI, USB

- Напряжение питания от 2.7 до5.5 В

Исходя из технического описания микросхемы, подберем вспомогательные элементы.

Из ряда Е12 выберем стандартные значения сопротивления резисторов

R1 = R3 = 22 Ом. Выберем тип резисторов С2-1 с допуском 10%.

Из ряда Е12 выберем стандартные значения сопротивления резисторов

R11 = R9 = 1 кОм. Выберем тип резисторов С2-3 с допуском 10%.

Из ряда Е12 выберем стандартное значение сопротивления резистора

R2 = 20 кОм. Выберем тип резисторов С2-2 с допуском 10%.

Из ряда Е12 выберем стандартные значения емкости конденсаторов С10 = С11 = 22 пФ. Выберем тип конденсатора К22-2 с допуском 10%.

Из ряда Е12 выберем стандартное значение емкости конденсатора С9 = 1 мкФ. Выберем тип конденсатора К50-2 с допуском 10%.

Для питания схемы выберем источник питания LM1117-5V.

Исходя из технического описания микросхемы, подберем вспомогательные элементы.

Из ряда Е12 выберем стандартные значения емкости конденсаторов С1 = С3 = 1 мкФ. Выберем тип конденсатора К50-1 с допуском 10%.

Из ряда Е12 выберем стандартное значение емкости конденсатора С4 = 4 мкФ. Выберем тип конденсатора К60-2 с допуском 10%.

7. Расчет параметров схемы, обеспечивающих заданные условия

Общая погрешность аппроксимации синусоиды складывается из погрешности дискретизации сигнала ![]() и погрешности нелинейности ЦАП

и погрешности нелинейности ЦАП ![]() .

.

![]()

Наиболее критичной в нашей схеме является погрешность погрешности линейности ЦАП, т. к. он является основой схемы. Выберем в качестве ЦАП микросхему AD9750 — 10 разрядный функционально законченный цифро-аналоговый преобразователь двоичного кода в ток, выполненный по тонкопленочной монолитной CMOS технологии и имеющий следующие характеристики:

Напряжение питания Uп =2,5 ÷ 5,5 В;

Погрешность нелинейности δЦАП = 0,1 %;

Выходное напряжение Uвых =0÷ Uп ;

Время установления выходного сигнала tуст =35 нс.

Микросхему ПЗУ надо выбирать по объёму памяти и времени выборки адреса.

В качестве ПЗУ остановимся на микросхеме КР556РТ181 емкостью 2K x 8 бит, обладающую следующими параметрами:

Время выборки адреса tв.а. = 25 нс;

Напряжение питания Uп = + 5 В.

Рассчитаем теперь общую погрешность нелинейности генератора:

![]() ,

,

![]() .

.

Полученная общая погрешность нелинейности не превышает заданного допустимого значения 0,2 %.

Заключение

В данном курсовом проекте были разработаны структурная и принципиальная схемы цифрового генератора сигналов треугольной, синусоидальной, прямоугольной формы с частотой от 1 Гц до 100 кГц с погрешностью нелинейности сигнала не более 0,112 %. Основным достоинством данного генератора является синхронизированность сигналов на его выходе. Также был произведен обзор существующих цифровых синтезаторов частоты.

Список литературы

[Электронный ресурс]//URL: https://inzhpro.ru/kursovaya/elektronika-i-mikroprotsessornaya-tehnika/

1. Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. — М.: 2008.

. Ашанин В.Н., Исаев С.Г., Ермаков В.В. Схемотехника: учебное пособие. — Пенза: Информационно-издательский центр ПГУ, 2007.

. Хоровиц П., Хилл У. Искусство схемотехники: учебное пособие. — М.: Мир, 1998.

. Стальбовский В.В., Четвертаков И.И. Резисторы: справочник. — М.: Советское радио, 1973.

. Техническая документация цифрового синтезатора AD9833 — Режим доступа: http://www.analog.com/static/imported-files/data_sheets/AD9833.pdf — электронная версия печатной публикации.

. Техническая документация микроконтроллера AT90USB162 — Режим доступа: http://www.atmel.com/Images/doc7707.pdf — электронная версия печатной публикации.

. Техническая документация источника питания LM1117-5V — Режим доступа: http://simplemachines.it/Datasheets_mizar/LM1117.pdf — электронная версия печатной публикации.

. Техническая документация усилителя OPA357-SOT23-6 — Режим доступа: http://www.ti.com/product/opa357ý — электронная версия печатной публикации.

. Якубовский С.В., Барканов Н.А., Ниссельсон Л.И. Аналоговые и цифровые интегральные микросхемы: Справочное пособие.: — М.: Радио и связь, 1984.

. Брамер Ю.А., И.Н Пащук. Импульсные и цифровые устройства. — М.:Высш. шк., 2003.